预览加载中,请您耐心等待几秒...

预览加载中,请您耐心等待几秒...

在线预览结束,喜欢就下载吧,查找使用更方便

如果您无法下载资料,请参考说明:

1、部分资料下载需要金币,请确保您的账户上有足够的金币

2、已购买过的文档,再次下载不重复扣费

3、资料包下载后请先用软件解压,在使用对应软件打开

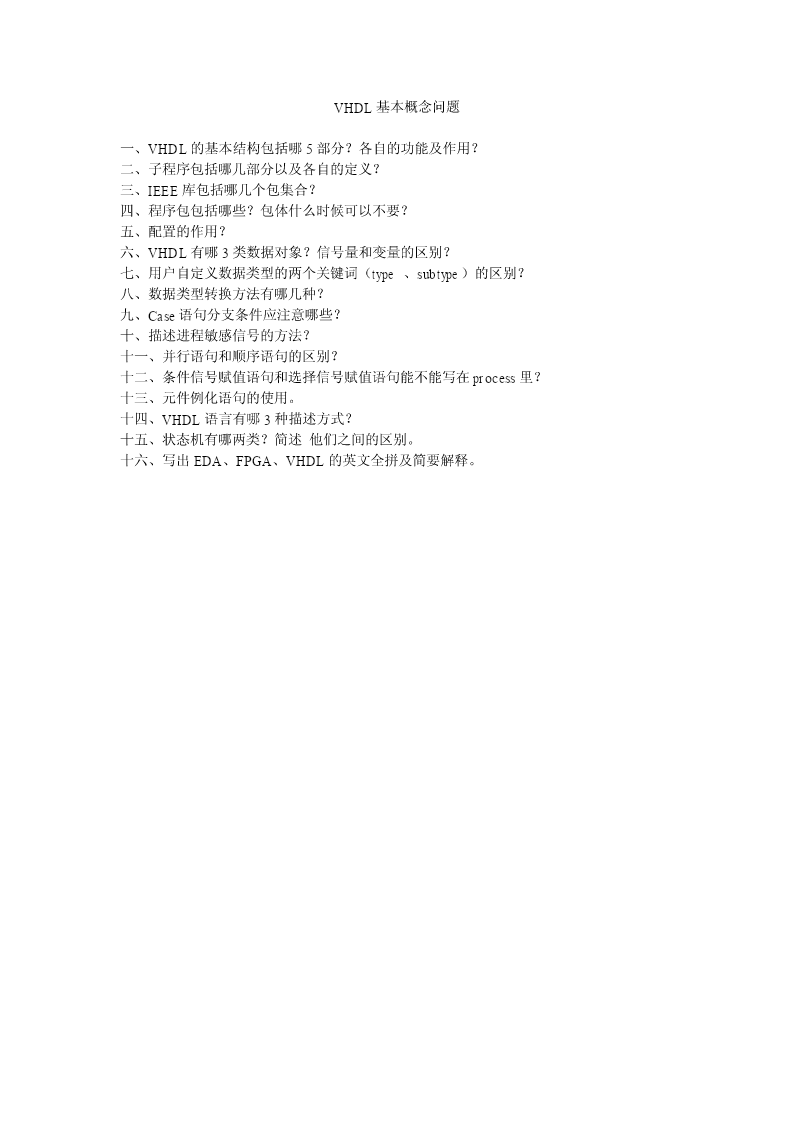

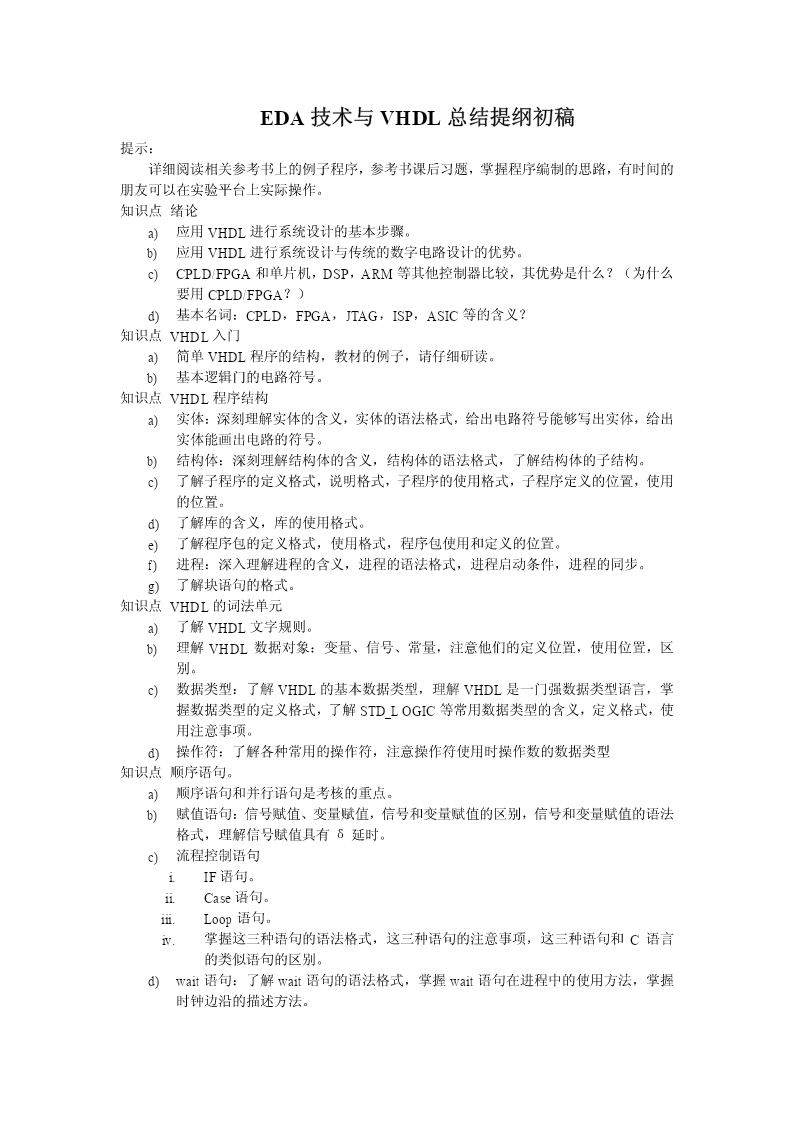

EDA技术与VHDL总结提纲初稿提示:详细阅读相关参考书上的例子程序,参考书课后习题,掌握程序编制的思路,有时间的朋友可以在实验平台上实际操作。知识点绪论a)应用VHDL进行系统设计的基本步骤。b)应用VHDL进行系统设计与传统的数字电路设计的优势。c)CPLD/FPGA和单片机,DSP,ARM等其他控制器比较,其优势是什么?(为什么要用CPLD/FPGA?)d)基本名词:CPLD,FPGA,JTAG,ISP,ASIC等的含义?知识点VHDL入门a)简单VHDL程序的结构,教材的例子,请仔细研读。b)基本逻辑门的电路符号。知识点VHDL程序结构a)实体:深刻理解实体的含义,实体的语法格式,给出电路符号能够写出实体,给出实体能画出电路的符号。b)结构体:深刻理解结构体的含义,结构体的语法格式,了解结构体的子结构。c)了解子程序的定义格式,说明格式,子程序的使用格式,子程序定义的位置,使用的位置。d)了解库的含义,库的使用格式。e)了解程序包的定义格式,使用格式,程序包使用和定义的位置。f)进程:深入理解进程的含义,进程的语法格式,进程启动条件,进程的同步。g)了解块语句的格式。知识点VHDL的词法单元a)了解VHDL文字规则。b)理解VHDL数据对象:变量、信号、常量,注意他们的定义位置,使用位置,区别。c)数据类型:了解VHDL的基本数据类型,理解VHDL是一门强数据类型语言,掌握数据类型的定义格式,了解STD_LOGIC等常用数据类型的含义,定义格式,使用注意事项。d)操作符:了解各种常用的操作符,注意操作符使用时操作数的数据类型知识点顺序语句。a)顺序语句和并行语句是考核的重点。b)赋值语句:信号赋值、变量赋值,信号和变量赋值的区别,信号和变量赋值的语法格式,理解信号赋值具有δ延时。c)流程控制语句i.IF语句。ii.Case语句。iii.Loop语句。iv.掌握这三种语句的语法格式,这三种语句的注意事项,这三种语句和C语言的类似语句的区别。d)wait语句:了解wait语句的语法格式,掌握wait语句在进程中的使用方法,掌握时钟边沿的描述方法。e)子程序调用语句:了解子程序调用的语法格式,理解子程序调用和C语言子程序调用的区别。f)了解其他语句,如属性函数等。g)复习本章课后习题。知识点并行语句a)理解进程并行的含义,理解进程顺序的含义。b)并行信号赋值语句的语法。i.简单信号赋值。ii.条件信号赋值语句。iii.选择信号赋值语句。iv.掌握他们的语法格式,掌握他们在使用过程中的注意事项。c)元件例化语句,掌握元件例化语句的语法格式,理解元件例化语句的含义,了解元件例化语句和子程序调用的区别。d)生成语句:理解生成语句的含义,了解生成语句的语法格式,与循环语句的区别。e)本章的课后习题。知识点状态机a)掌握状态机程序的结构。b)了解最典型状态机程序的特点。c)详细阅读本章的例子程序。d)详细完成本章课后习题。EDA实验室VHDL基本概念问题一、VHDL的基本结构包括哪5部分?各自的功能及作用?二、子程序包括哪几部分以及各自的定义?三、IEEE库包括哪几个包集合?四、程序包包括哪些?包体什么时候可以不要?五、配置的作用?六、VHDL有哪3类数据对象?信号量和变量的区别?七、用户自定义数据类型的两个关键词(type、subtype)的区别?八、数据类型转换方法有哪几种?九、Case语句分支条件应注意哪些?十、描述进程敏感信号的方法?十一、并行语句和顺序语句的区别?十二、条件信号赋值语句和选择信号赋值语句能不能写在process里?十三、元件例化语句的使用。十四、VHDL语言有哪3种描述方式?十五、状态机有哪两类?简述他们之间的区别。十六、写出EDA、FPGA、VHDL的英文全拼及简要解释。